連于慧 2025.5.15

2021年以前,台積電的技術論壇主軸是「手機」(最早應用分類是統稱為通訊類),智慧型手機帶給科技產業的黃金年代持續了約莫15年。直到2022年首季,高性能運算HPC在台積電的營收分類比重上,首度超過手機,象徵的科技時代的轉折點。但當時應該沒有人預測,接下來生成式AI井噴式的大爆發,讓全世界都措手不及,不僅改變科技產業的行進路線,更顛覆整個人類的生活樣貌。

毫無疑問,台積電技術論壇上的主軸是「AI」(可能未來20?年都是)。台積電亞洲業務處長萬睿洋指出,2024年AI拿下兩個諾貝爾獎:一是有人工神經網路機器學習領域的開創性發現與發明,拿下2024年的諾貝爾物理獎; 二是同年諾貝爾化學獎得主是以AI演算來預測和合成蛋白質,成功提高新藥和疫苗的開發。揭示AI時代的來臨,未來AI發展會從生成式AI、代理AI,進展到實體AI。

萬睿洋表示,未來生成式AI將改變我們40%的日常活動,大家會開始習慣使用多模態大型語言模型實現影片、文字、語音等等來生成內容、數據彙整、預測功能,為我們簡化決策和提升生產力。再來,預計2028年之前,代理AI將處理我們超過15%的工作,日常生活像是協助我們訂機票、找最佳航班、規劃旅遊且確保所有行程銜接等等。第三個階段是進入實體AI,也就是原型機器人、自駕車的時代,預計到2035年會有13億台AI機器人運用在真實世界,2050年更會有40億台機器人,其中有6.5億台會是人形機器人。再者,全球AI機器人產值在2030年將突破350億美元,到了2030年,每10輛汽車中,就會有1台是自動駕駛。

張曉強指出,2024年是AI元年,2025年繼續且非常強勁,運用到5nm、4nm、3nm製程。對於汽車產業,。雖然這一年來很疲軟,但因為自駕功能,在半導體應用加速採用晶片,ADAS大多數採用12nm和8nm製程,未來進入5nm和3nm製程。汽車可以說是第一部機器人,再來是人型機器人,未來需要非常多的半導體晶片。現在很多汽車製造商正在將汽車的概念延伸到機器人領,人形機器人需要極高的智慧程度,這來自於先進的處理器,需要大量的複雜電子零件和先進軟體來實現功能,例如模仿人手動作,未來的機器人需要達到 10 倍的進步,也需要更先進製程技術。

為什麼AI會帶動先進製程高速成長? 張曉強表示,主要是能源效率。因為半導體製程技術不斷推進以及設計架構的演進,能源效率大約每兩年會提升三倍,使得能源效率被認為是未來 AI 發展最重要的基礎。

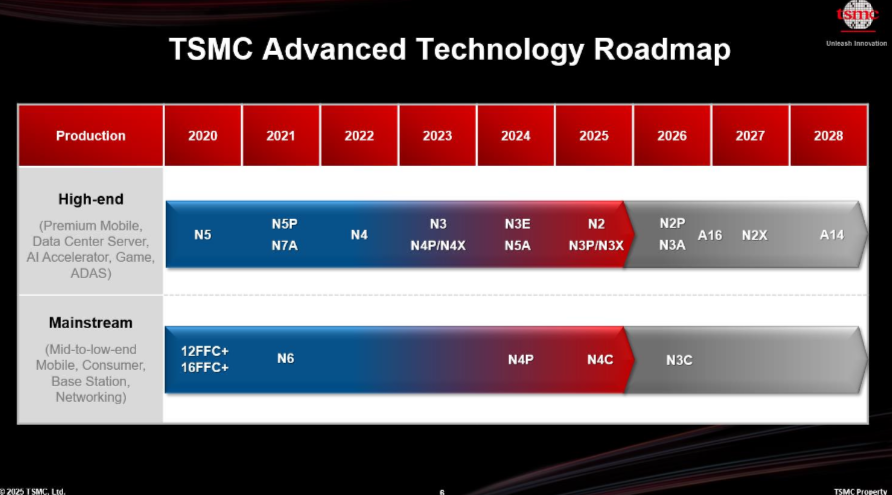

- 先進製程發展進度:

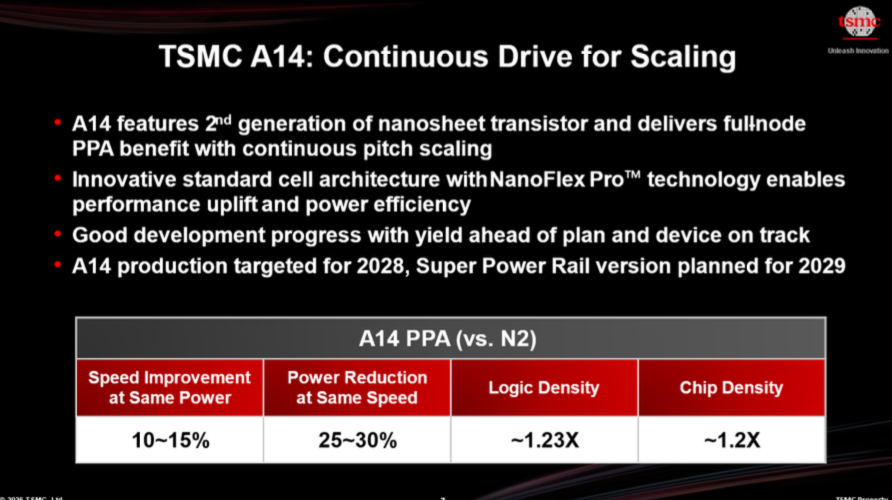

將採用新的 NanoFlex Pro 技術, 計劃於 2028 年開始生產,搭載超級電軌技術(Super Power Rail, SPR)的版本則計劃於 2029 年推出。

▪ A16製程:

適合對訊號路由和供電要求嚴苛的資料中心AI/HPC 產品,為其提供業界最佳的背面供電技術和優化的邏輯密度,計劃於 2026 年下半年量產。

▪ 2奈米製程:

2025 年下半年量產,目前256Mb 的 SRAM 其平均良率超過 90%, N2第二年的新設計定案(tape-outs)數量比同期的 N5 增長了 4 倍。依計畫在 2026 年下半年量產。N2X將提供約 10% 的 Fmax(最大時脈頻率),並計劃於 2027 年量產。

▪ 3 奈米製程:

預計是一個高產量且長期生產的技術,截至 2025 年 4 月,已有超過 70 個新的設計定案。

▪ 超越 N2 的技術創新:

互補式場效電晶體(CFET)設計是很有前景的微縮技術候選,可滿足越來越多在緊湊外形尺寸中提高效能和降低功耗的需求。透過將 nFET 和 pFET 垂直堆疊,CFET 實現了近兩倍的電晶體密度。在今年的 IDEM 上,台積電將 nFET 和 pFET 整合於同一晶圓中,並展示了具備 48 奈米閘極間距、世界上最小的 CFET 逆變器。台積電亦在採用 2D 材料的電晶體方面取得了進展,發展出研究組合中最薄的電晶體通道,展示了首個在類似於 N2 技術的堆疊奈米片電晶體架構中,採用單層通道的電氣性能。

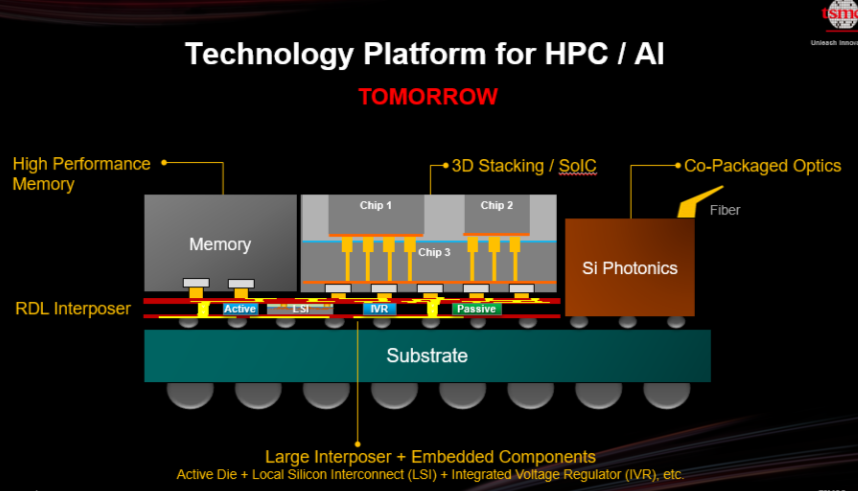

▪ 3DFabric技術:

SoIC 平台:用於 3D 矽堆疊,由 SoIC-P 和 SoIC-X 兩種堆疊方案組成。用於 N3-on-N4 堆疊的 SoIC 技術將於 2025 年進入量產,其間距為 6μm。下一世代 SoIC A14-on-N2 將於 2029 年就緒。

InFO PoP 和 InFO-3D:針對高階行動應用,InFO 2.5D 則用於 HPC 的小晶片整合。

作為 AI 訓練和推理的關鍵驅動因素,基於矽中介層的 CoWoS-S 和基於 RDL 中介層的 CoWoS-L 和 CoWoS-R 旨在為 HPC 應用整合先進邏輯和 HBM。

更大的光罩尺寸使更多的晶圓可以整合到同一個封裝中。這樣可以更有效地將多個較小的晶片(小晶片)和記憶體堆疊(如 HBM)整合到一個單獨且較大的中介層上。

5.5 倍光罩尺寸的 CoWoS-L 技術將於 2026 年推出。正在透過 9.5 倍光罩尺寸的 CoWoS 突破界限,計劃於 2027 年量產,此一尺寸可在一個封裝中整合 12 個或更多的 HBM 堆疊,結合先進邏輯技術,支援更大的 AI 加速器設計。

▪系統級晶圓(TSMC-SoW)技術:

邏輯和 HBM 晶圓級整合,滿足 AI 訓練對運算能力激增的需求。SoW 平台將所有必要的元件整合在一起,例如連接器、電源模組和冷卻模組。 SoW-X是一款基於 CoWoS 技術和晶圓尺寸的系統,其運算能力比現有的 CoWoS 解決方案高 40 倍,與整座伺服器機架相當,SoW-X 計劃於 2027 年量產。

- 智慧車輛技術:

▪用於毫米波雷達的 16FFC 射頻製程技術下一代電阻式隨機存取記憶體(RRAM)和磁阻式隨機存取記憶體(MRAM)

▪ 28 奈米的 RRAM 已通過汽車應用認證,並預期 12 奈米的 RRAM 亦將滿足同樣嚴苛的汽車低 PPM 要求。

▪ 22 奈米 MRAM 已進入量產,16 奈米 MRAM 已為客戶準備就緒。並正在開發 12 奈米的 MRAM。

▪ 正在驗證 MRAM 和 RRAM 分別縮至 5 奈米和 6 奈米的未來可擴展性。

- 物聯網技術:

- 射頻技術:

- 台積電小知識:

▪ 到 2030 年,半導體市場將達到 1 兆美元,由HPC占45%、智慧型手機25%、汽車15%和物聯網10%。

▪ 2025 年與 AI 相關產品的晶圓出貨量預計將是 2021 年的 12 倍之多。

▪ 2025 年大尺寸晶片的產品出貨量預計將是 2021 年的 8 倍。晶片尺寸越大,管理生產良率的挑戰就越高。

▪ 在先進封裝領域,從 2022 年到 2026 年,SoIC 產能增長的年複合成長率(CAGR)將超過 100%,CoWoS 產能增長的年複合成長率將超過 80%。