今天台積電技術論壇上,2024年3月升任共同營運長,現任台積電業務開發、海外營運辦公室資深副總暨副共同營運長的張曉強現場金句連發:

- 台積電做系統整合超過20年,領先推出CoWoS技術,我相信在座各位都可以拼出C-o-W-o-S-.......有天我發現連電視台主播都會拼這個詞,你要是沒聽過CoWoS,大概是外星人了!

- 過陣子也不用我和Cliff上台來演講了,create一個AI來講就好!

- (現場張曉強show出一張PPT標誌著Nvidia近代GPU產品採用台積電製程技術的性能成長曲線直線向上)他說:AI發展快速,Nvidia產品從V100採用N12、A100採用N7、H100採用N4,一直最新一代Blackwell採用N4P製程+CoWoS封裝讓算力成長1000倍,這迅猛的長曲線讓人想到了昨晚的Nvidia股價.......

- 台積電今日技術論壇中,現場含金量最高的一張圖應該是3D Integrated HPC Technology platform for AI。張曉強說這張圖是“Money Sheet”(既然價值連城,就不在此大放送!其實是因為現場是禁止攝影)從現場的圖上看,是一款用于HPC和AI的新封裝平台,並以矽光子來改善互聯。他表示矽光子技術已經量產,只是這是第一次引入HPC中,用在Data Center。

- 如果有人要寫台積電歷史,一定要提到7nm,這是台積電第一次提供全世界最先進的技術,在此之前都是IDM。之後台積電在2020年更領先進入5nm製程,2023年進入3nm製程。

以下是今日舉行台灣場的技術論壇幾個重點:

- AI將掀起第四次工業革命,2030年全世界將有10萬個生成式AI機器人,生成式AI手機出貨量將達2.4億支。

- 為了滿足AI運算需求,3D堆疊、先進封裝技術越來越重要,未來幾年將實現單晶片上整合超過2,000億個電晶體並透過3D封裝達到超過一兆個電晶體。

- 2024年3nm產能比2023年增加三倍,但還是不夠用!!

- 2020~2024年,先進製程產能的年複合成長25%,特殊製程產能的複合成長率10%。車用晶片出貨複合成長率約50%。

- SOIC在2022~2026年的產能複合成長100%,CoWoS在2022~2026年的產能複合成長超過60%

- 台積電從2019年正式使用EUV設備,目前全球56%的EUV機台都在台積電。

- N3E已依計畫在2023年第四季進入量產,客戶的產品良率相當好。台積電也開發出N3P技術,已通過驗證,目前良率表現接近於N3E。N3P已經收到了客戶產品設計定案tape-outs,將於 2024 年下半年開始量產。

- 2nm是台積電第一次使用奈米片Nano-Sheet電晶體架構,目前進展非常順利,NanoSheet奈米片的轉換目標達90%,換成良率也超過80%,根據計畫2nm是2025年下半年量產。

- 針對製程後段,會導入新製程與材料,將電阻/電容延遲(RC delay)降低高達10%。此外,為了強化功率傳輸,台積電也提供了超高性能金屬/絕緣體/金屬電容(SHPMIM),其容量密度是上一代技術的兩倍之多。

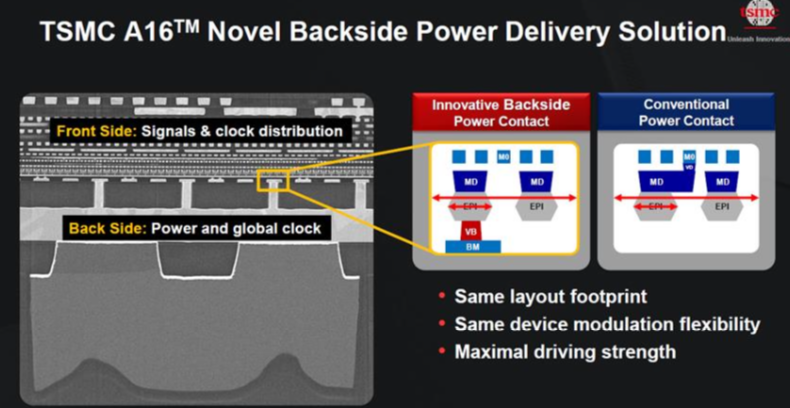

- 台積電進入埃米(angstrom)時代的A16,結合2nm製程+超級電軌(Super Power Rail)架構設計。

- A16 技術的超級電軌(Super Power Rail)架構是一種創新的最佳晶圓背面供電網路解決方案。A16 將供電網路移到晶圓背面而在晶圓正面釋出更多訊號網路的佈局空間,藉以提升邏輯密度和效能。此外,它還可以改善功率傳輸,並大幅減少IR 壓降。

- 再者,台積電的創新晶圓背面傳輸方案也是業界首創,保留了柵極密度與元件寬度的彈性,是具有複雜訊號佈線及密集供電網路的HPC產品的最佳解決方案。相較於台積公司的 N2P 製程,A16 在相同 Vdd (工作電壓)下,速度增快8~10%; 在相同速度下,功耗降低15~20%,晶片密度提升高達 1.10X。台積電計畫在 2026 年下半年量產。

- NanoSheet奈米片電晶體的下一代會是互補式場效電晶體CFET架構,藉由不同材料的上下堆疊,讓垂直堆疊的不同場效電晶體更靠近,改善電流且密度增加1.5~2倍。台積電強調CFET不是紙上談兵,研發已經成功驗證在wafer siliocon上。

- 台積電指出,當電晶體架構從平面式(planer)發展到 FinFET,並即將轉變至奈米片(nanosheet)架構之後,公司認為垂直堆疊的 nFET 和 pFET (即互補式場效電晶體CFET)是未來製程架構選項之一。

- 台積電進一步指出,內部一直在積極研究將 CFET 用於未來製程架構的可能性。在考量佈線和製程複雜性後,CFET 密度將可提升 1.5 至 2X,除了 CFET,在低維材料方面取得了突破,也可實現進一步的尺寸和能源微縮。再者,台積電也計畫導入新的互連技術,以提升互連效能。首先,對於銅互連技術,計畫導入一個全新的通路結構(via scheme),進而將業界領先的通路電阻(via resistance)再降低 25%。再者,計畫採用一種全新的通路蝕刻停止層(via etch-stop-layer),可降低約6%的耦合電容。還有,正在研發一種新的銅阻障方案(Cu barrier),可降低約 15%的銅線電阻。除銅互連外,台積電也在研發一種含有氣隙的新型金屬材料,可降低約 25%的耦合電容。另外,嵌入石墨烯(Intercalated graphene)也是一種極具前景的新材料,可大幅縮短互連延遲。

TSMC 3DFabricTM技術方面,包含三大平台:TSMC-SoIC、CoWoS和InFO。

- SoIC 平台:用於 3D 矽晶片堆疊,並提供 SoIC-P 和 SoIC-X 兩種堆疊方案。SoIC-P是一種微凸塊堆疊解決方案,適用於講求成本效益的應用如行動裝置。CoWoS 平台包括成熟度最高、採用矽中介層的 CoWoS-S,以及採用有機中介層的CoWoS-L 和 CoWoS-R。InFO PoP 和 InFO-3D 適用於高階行動式應用,InFO 2.5D 則適用於高效能運算的小晶片整合。另外,根據產品需求,SoIC 晶片可與 CoWoS 或 InFO 整合。

- 適用於 3D 小晶片堆疊技術的 SoIC:SoIC-X 無凸塊堆疊解決方案,無論是現有的 9 微米鍵合間距前到後堆疊方案(front-to-back scheme),還是將於2027 年上市的 3 微米鍵合間距前到前堆疊方案(front-to-front scheme),裸晶到裸晶(die-to-die)互連密度均比 40 微米到 18 微米間距的微凸塊前到前堆疊方案高出 10X 以上。台積電的SoIC-X 技術非常適用於對效能要求極高的各類HPC應用。

- 台積電更指出,看到客戶對於 SoIC-X 技術的需求逐漸增加,預計到 2026 年底將會有 30 個客戶設計定案tape-outs。

- CoWoS 技術:可將先進的 SoC 或 SoIC 晶片與先進的高頻寬記憶體HBM進行整合,滿足AI 晶片的嚴苛要求。台積電的SoIC 已透過 CoWoS-S 量產出貨,並計畫開發一種 8 倍光罩尺寸且具備採用A16 製程技術的 SoIC 晶片和 12 個HBM堆疊的 CoWoS 解決方案,計將在 2027 年開始量產。直至今年年底,台積公司將為超過 25 個客戶啟動超過 150 個 CoWoS 客戶產品設計定案tape-outs。

- 台積電與Nvidia合作推出Blackwell AI 加速器,是全球首款量產並將 2 個採用 5 奈米製程技術的 SoC 和 8 個HBM堆疊整合在一個模組中的 CoWoS-L 產品。

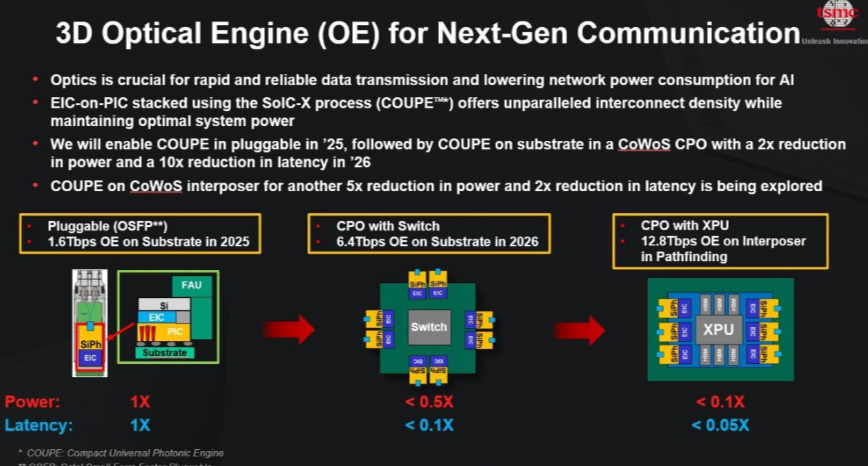

- 矽光子:台積電表示矽光子是共同封裝光學元件CPO的最佳選擇,因為其與半導體相容,且可與 EIC/PIC/交換器在封裝層高度整合。台積電創新的緊湊型通用光子引擎(COUPETM)技術透過最短路徑的同質銅-銅介面整合電子積體電路(PIC)和光子積體電路(EIC),進而實現超高速射頻(RF)訊號(200G/λ)。

- COUPE 解決方案可最小化使用面積,且具備光柵耦合器(GC)和邊際耦合器(EC),可滿足客戶的各式需求。台積電計畫在 2025 年完成小型插拔式連接器的 COUPE 驗證,2026 年將其整合於共同封裝光學元件的 CoWoS 封裝基板,藉此可降低 2X 功耗、將延遲降低10X。同時,台積電也探索一種更先進的共同封裝光學元件方案,將 COUPE 整合於 CoWoS中介層,進而將功耗再降低 5X、將延遲再降低 2X。

相關新聞:

50%關稅加上去,恐讓中國成熟製程產能過剩更嚴重,「國產化」速度勢必提前

AI PC大戰開打,高通拿下首局勝利